本文介紹一個基于Spirit_V4開發板、使用Quartus II軟件設計與開發的高精度秒表倒計時器系統。該系統采用Verilog HDL硬件描述語言進行模塊化設計,實現了秒表(正計時)、倒計時、暫停、復位等核心功能,精度可達0.01秒(10ms)。

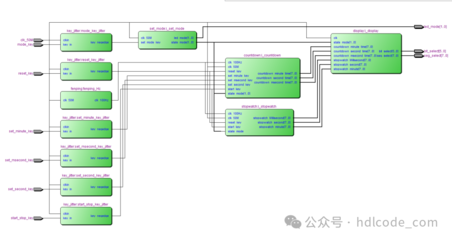

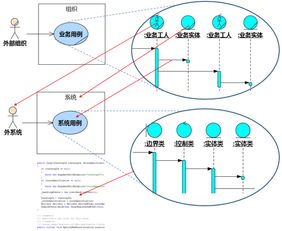

一、 系統總體架構

該系統采用自頂向下的設計方法,主要包含以下功能模塊:

- 頂層模塊 (top_timer):實例化并連接所有子模塊,定義與開發板物理資源(時鐘、按鍵、數碼管、LED)的接口。

- 時鐘分頻與使能生成模塊 (clk_gen):將板載50MHz主時鐘進行分頻,產生全局時序控制所需的10ms(100Hz)基準時鐘使能信號,確保計時精度。

- 核心計時與控制模塊 (timer_core):系統的核心狀態機。根據按鍵輸入,在“秒表模式”、“倒計時模式”、“暫停”、“復位”等狀態間切換,并執行相應的計數邏輯。

- 按鍵消抖模塊 (key_debounce):對機械按鍵產生的抖動信號進行濾波,確保每次按鍵只產生一個穩定的有效脈沖。

- 數碼管動態掃描驅動模塊 (seg_driver):將計時器產生的BCD碼時間數據(時、分、秒、0.01秒)轉換為七段數碼管段選信號,并通過時分復用方式驅動多位數碼管顯示。

- LED指示模塊 (led_indicator):根據系統當前工作模式(如運行、暫停、倒計時結束),控制LED燈給出直觀的狀態指示。

二、 關鍵模塊Verilog代碼設計要點

1. 時鐘分頻模塊 (clk_gen)

module clk_gen(

input clk_50m, // 50MHz時鐘

input rst_n, // 異步低電平復位

output reg clken10ms // 10ms使能脈沖

);

reg [19:0] cnt; // 50M / 100 = 500,000, 需要19位計數器

always @(posedge clk50m or negedge rstn) begin

if (!rst_n) begin

cnt <= 20'd0;

clken10ms <= 1'b0;

end

else begin

if (cnt == 20'd499_999) begin // 計數到499999,產生一個周期的高脈沖

cnt <= 20'd0;

clken10ms <= 1'b1;

end

else begin

cnt <= cnt + 1'b1;

clken10ms <= 1'b0;

end

end

end

endmodule2. 核心計時與控制模塊 (timer_core) 狀態機設計

該模塊定義了三個主要狀態:IDLE(復位/初始)、RUN(計時運行)、PAUSE(暫停)。在RUN狀態下,根據模式選擇信號mode(來自按鍵),決定是進行正計時累加還是倒計時遞減。倒計時初值可通過預置寄存器設置,當倒計時減至零時,產生結束信號并觸發LED警報。

3. 按鍵消抖模塊 (key_debounce)

采用經典的計數器消抖法。當檢測到按鍵電平變化后,啟動一個約20ms的計時器,在此期間持續采樣,若電平保持穩定,則輸出有效的按鍵脈沖。這能有效濾除機械觸點閉合/斷開時產生的5-10ms抖動。

4. 數碼管驅動模塊 (seg_driver)

該模塊將內部存儲的24位時間數據(格式為:HH-MM-SS-MS,每4位為一個BCD碼)按位分離,并通過一個高速掃描計數器(約1KHz)循環選中每一位數碼管,同時輸出對應的段碼數據,利用人眼視覺暫留實現穩定顯示。

三、 Quartus II工程開發流程

- 新建工程:指定工程目錄、器件型號(對應Spirit_V4開發板上的FPGA,如Cyclone IV EP4CE10F17C8)。

- 設計輸入:創建Verilog源文件,編寫上述各模塊代碼。

- 分析與綜合:Quartus對代碼進行邏輯綜合,生成門級網表。

- 引腳分配:根據Spirit_V4開發板原理圖,將設計中的輸入輸出信號分配到具體的物理引腳(如時鐘引腳、按鍵引腳、數碼管段選/位選引腳、LED引腳)。這是硬件實現的關鍵一步。

- 全編譯:執行完整的編譯流程,包括綜合、布局布線、時序分析和編程文件生成。

- 時序仿真(可選但推薦):使用ModelSim等工具進行功能仿真,驗證計時精度、按鍵響應和狀態切換邏輯的正確性。

- 板級調試與下載:通過USB-Blaster將生成的

.sof或.jic文件下載到Spirit_V4開發板中,進行實際功能測試。

四、 功能測試與性能分析

在實際測試中,系統應實現以下功能:

- 秒表模式:按下“開始/暫停”鍵開始正計時,再次按下暫停,可隨時復位。

- 倒計時模式:通過模式鍵切換至倒計時,可預置時間(例如通過撥碼開關或組合按鍵設定),啟動后開始遞減,歸零時蜂鳴(或LED閃爍)報警。

- 高精度顯示:穩定顯示

00:00:00.00至99:59:59.99的時間范圍。

系統精度主要由10ms使能信號的穩定性決定,該信號源于50MHz晶振,誤差極小,完全滿足常規高精度計時需求。

五、

本項目完整展示了使用Verilog HDL在FPGA平臺上設計一個數字系統的流程。通過模塊化設計、狀態機控制、時鐘管理、人機接口(按鍵、顯示)驅動等技術的綜合運用,成功在Spirit_V4開發板上實現了一個功能完善、性能穩定的高精度秒表倒計時器。該設計方法可進一步擴展,如增加多組計時存儲、串口通信上位機控制等功能,具有良好的教學意義和實踐價值。